- 12/11

- 2017

-

QQ扫一扫

-

Vision小助手

(CMVU)

坦白说,Digilent Nexys Video开发板可能是市面上性价比最高的音视频处理FPGA口袋实验室了。作为一款专用于音视频处理教学以及视频和视觉应用原型开发的评估板,此板搭载了Xilinx Artix-7系列中资源最大的器件Aritx-7 XC7A200T FPGA。

今天我们就来介绍一下如何使用Nexys Video来实现一个简单的HDMI输入/输出视频处理系统。先来看下此板所集成的支持视频接收、处理和生成/输出的下列I/O和外设接口:

HDMI输入

HDMI输出

显示输出端口

以太网

UART

USB

512MB DDRSDRAM

线路输入(Line In)/麦克输入/耳机输出/线路输出(Line Out)

FMC

使用VHDL与RTL方法,要创建一个简单的图像处理流水线,我们需要实现如下架构:

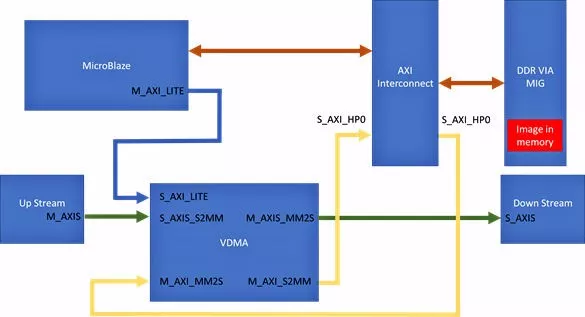

监控处理器(本例中采用Xilinx Artix-7 FPGA实现的MicroBlaze软核RISC处理器)用于监控与用户接口间的通信并根据应用的要求配置图像处理流水线。在本例这个简单的架构中,HDMI输入口接收的数据从原始的并行格式的视频数据、Hsync和VSync转换为AXI Streaming(AXIS)格式。我们想要将数据转换成AXIS格式是因为Vivado提供多个使用这种数据格式的图像处理IP。如果我们使用Vivado HLS来创建我们自己的图像处理模块,那么能够支持AXIS接口也很重要。

MicroBlaze处理器需要支持如下外围设备:

AXI UART – 支持系统的通信和控制

AXI Timer – 使MicroBlaze可以实时运行事件

MicroBlaze调试模块 – 支持MicroBlaze的调试

MicroBlaze本地存储 – 连接到DLMB和ILMB(数据&指令本地存储总线)

我们将使用存储接口生成器来创建与板上SDRAM对接的DDR接口。这个接口和SDRAM创建了一个公共的存储框架,可以访问图像处理管道以及使用AXI interconnect访问监控处理器。

创建一个简单的图像处理流水线需要使用如下IP:

DVI2RGB – Digilent提供的HDMI输入IP

RGB2DVI – Digitlent提供的HDMI输出IP

Video In to AXI4-Stream – 将并行视频输入转换为AXI Streaming协议(Vivado IP)

AXI4-Stream to Video Out – 将AXI-Stream转换为并行视频输出(Vivado IP)

Video Timing Controller Input – 检测输入视频流参数(Vivado IP)

Video Timing Controller Output – 生成输出视频流时序参数(Vivado IP)

Video Direct Memory Access – 支持图像写入和从DDR SDRAM读出

视频处理链的核心是VDMA,我们借助它来将图像移动到DDR内存中。

上图展示了IP如何将流式数据转换为读和写管道中内存映射的数据。两个VDMA通道都提供了在流式数据和内存映射数据之间转换的能力。写通道支持流到内存映射的转换而读通道提供内存映射到流的转换。

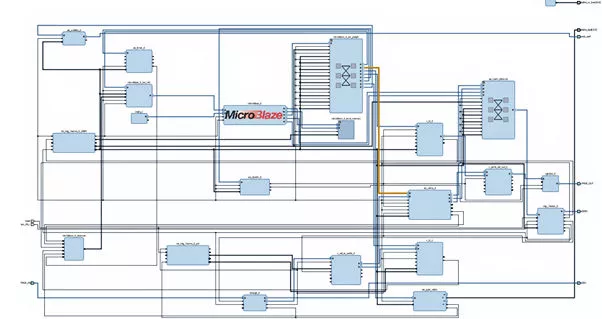

当把所有这些集中到Vivado中创建初始的基本系统,我们得到了如下架构,这是Nexys Video HDMI示例提供的。