- 07/01

- 2019

-

QQ扫一扫

-

Vision小助手

(CMVU)

在无线电系统中应用数字波束成形,需要同时采样天线阵列的低层信号。这需要保存信号到达每个天线节点的空间信息。 虽然这种方案复杂度较高,会带来额外的功耗,但其也具有一些显著的优点:

. 高信噪比(SNR)帮助提高无线链接容量,从而增加信号范围

. 使用天线阵列的空间特性避免干扰。因为干扰来自某个特定方向,波束成形算法可使用零位技术消除干扰。

. 高效率、大容量的无线链路意味着雷达系统可同时追踪多个目标,或移动电话网络可支持多个通话。

今天,很多应用使用波束成形,或者至少需要同步采样。但是,在GHz频率下工作时, IC和板级的信号的传播时

间都非常重要。PCB走线被用于传输线,因此需保证信号线长度匹配以保持相位信息。每厘米的线长将增加60到

75ps的传递时间。将其与6GHz采样时钟的166ps时钟周期相比,可以看出板级的效应会极大影响设计。这解释

了为什么在高速采样系统中PCB布线是一个关键的因素。但是,还有另外一个因素会使设计变得困难,这个因素

和时域有关,称为亚稳态。

同步链为ESIstream带来确定的延迟

亚稳态描述了数字电路中的一种不确定的状态,随着采样率的提高,它成为了潜在的系统时序问题的一个重要原因。用户需用同步的方法对抗亚稳态,这正是引入同步链的方案的原因。

用户需要一种可靠且简单的同步时序实现方法。在Teledyne e2v,确定性同步围绕着一对事件驱动的差分电信号建立:同步和同步输出信号(SYNCTRIG和SYNCO)。这些信号保证目标转换器的时序系统可被复位,并且所有的数

字子系统都被恰当地锁定到主参考时钟。另外,这种同步方案可扩展到大系统中的多个ADC。

这种方案的优点在于非常简单——它无需额外的时钟信号,可保证系统生命周期内多个并行通道的同步。一旦设计完成准备生产,可使用一个训练序列建立正确的系统同步。如果环境条件变化,比如温度或电压变化,系统时序参

数保持不变。同步链提供了一个非常可靠的同步源,这对产品量产是一个巨大的优势。

然后,为了实现确定性延迟,在ESIstream链路的接收端有一个简单的计数器和接收弹性缓冲,用于补偿传递过程的最大线路延迟不确定度。

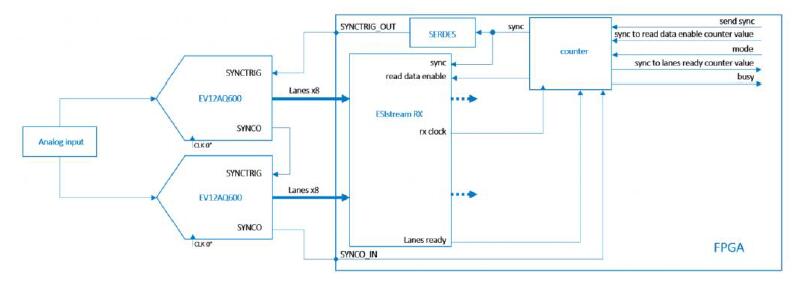

图 9 ESIstream接收器中的帧计数器的位置

FPGA内部的计数器模块计算SYNCTRIG上升沿事件和“所有线路接收准备好”事件之间的Rx的时钟数。这些信息和弹性接收缓冲允许整个系统的接收数据对齐。这样,利用ESIstream的产品带有的信号链功能,将确定性行为扩展到整个使用ESIstream的系统中的方法是可行的。

ESIstream VHDL模块——发展的目标

为了使ESIstream更加易于使用,Teledyne e2v的提出者Teledyne e2v在2018年底启动了一个项目,研发ESIstream Tx和Rx的IP模块,用于行业内FPGA厂家(包括Xilinx和Intel)提供的通用FPGA。IP将支持不同的运行速度,且适用于包括宇航级在内的不同等级的应用。毋庸置疑,IP的重点在于为Teledyne e2v现有的产品系列提供匹配的性能。为了实现这个固定功能的IP,Teledyne e2v在底层做了很多工作以动态定义可配置的线速率模块,包含一系列广泛的数据转换器采样频率,并支持更多可定义的功能。

串行化的未来

Teledyne e2v未来的开发计划还包括用于ESIstream物理层的光纤应用。光纤允许转换器被放置在距离FPGA很远的地方,而不是基于铜线的接口(PCB走线或同轴电缆)。通过将两块Xilinx VC709评估板使用四个SFP (小型可插拔) 光线路连接并运行在6Gsps的速度,证明了上述的特性。

图 9 使用物理层的光纤演示ESIstream Tx和Rx

在经过完整的测试和认证后,VHDL代码模块将被放置在网站上,供用户免费下载。

ESIstream和JEDEC对比

ESIstream的系统级优点可简单概括如下:

. 无需每个器件的LMFC时钟,无需LMFC时钟的对齐操作。

. 当使用单个器件或采用同步链同步多个器件时,无需考虑ESIstream同步信号的PCB线长匹配。

. 无需SYSREF,因此与JESD204B相比,ESIstream降低了硬件复杂度,实现了确定性操作。

. ESIstream系统中的确定的同步行为是通过一种叫做同步训练的特性(请参考其他文档)实现的。ESIstream

仅需要一次系统的训练。一旦得到延迟参数,对于给定的设计这些延迟参数将维持不变。这意味着ESIstream

是一种易于量产化的接口。

结语

JESD204B子集1和2里描述的JEDEC数据串行化方法似乎解决了多通道数据转换器系统的确定性操作的挑战。

这在一定程度上无疑是正确的,但是通常被忽视的是设计师在处理复杂传输和规格物理层需求时遇到的众多挑战。

工程师通常认为用于信号处理SoC(FPGA或ASIC)的JESD204B许可证和核心IP可帮助解决大多数设计上的问题。

但是,据报道,很多事实和经验表明,JESD204B引入的多域时钟复杂度的时序约束,给PCB的设计带来了很大

的麻烦。

还有另外一个方法。ESIStream。ESIStream是一个开源免费的协议。它与JESD204B的性能等级相同,但能带来

更好的用户体验。低复杂度,易于设计,低功耗。现在,随着用于工业标准FPGA的Rx和Tx的IP模块和VHDL

代码模块的发布,大大降低了ESIstream的使用难度。目前IP模块在开发阶段,会支持Teledyne e2v新数据转换

器的规格。另外,用户可免费下载适用于自己的高速串行项目的VHDL代码模块。

关于Teledyne e2v

Teledyne e2v的创新引领着医疗、生命科学、宇航、运输、国防、安全和工业市场的发展。Teledyne e2v特有的

方法包括了解市场和用户应用的挑战,然后与用户合作,提供创新的标准化、半定制或全定制的解决方案,为用户

的系统带来价值增长。Teledyne e2v拥有世界领先的再设计和向上筛选的商业技术,与NXP有超过30年的战略

合作关系,开发NXP商业处理器的宇航级、军级和工业级版本。Teledyne e2v可获取原始测试向量,保证基于

QorIQ. Power. 架构系列产品的高可靠性,而且其正在研发基于NXP Layerscape系列的解决方案。