- 02/12

- 2020

-

QQ扫一扫

-

Vision小助手

(CMVU)

关于新兴内存如何掌握物联网(IoT)创造的机会而无需使用SRAM等昂贵的内存方案,一直都有很多的讨论。对此,采用“低接脚”(low-pin)的DRAM可能会是理想解决之道。

钰创科技(Etron Technology)成像与内存产品开发副总裁兼首席科学家Richard Crisp说,该公司的DRAM新架构展现了不同于JEDEC发展蓝图的传统架构,能够满足无需越来越高密度、高接脚速度或最新DDR4 (最小容量4位)中所有可用带宽的应用需求。“目前还有许应用采用不到1Gbit的内存。人们对于简单易用且容量适中的内存更感兴趣。”

Crisp说,这正是Etron的原动力,该公司着眼于提供容量恰好够用的DRAM来满足应用需求,同时减少典型DDR内存的接脚数。当该公司走向开发小尺寸、低接脚数内存的道路之时,业界也开始变得对人工智能(AI)感兴趣。“我们一开始时并没真正考虑过AI,但这确实发生了,没想到刚好为此带来了一款有趣的解决方案。”

典型的AI应用场景之一是在端点收集各种数据后发送到集中式云端,以连接两端的大型网络层进行处理。但是,Crisp解释,Etron则在端点和边缘之间进行差异化——端点是由传感器收集来自外在世界的资料,而边缘则是本地的集中式处理计算机,能以相当高性能的媒体处理器,将多个传感器的数据汇聚到公共串流中。他说,在发送情报至云端之前,位于边缘的计算机将会先在此串流上自行分析,因而需要比端点更高的性能。

Crisp说,Etron为此设计了减少接脚数(RPC)的DRAM,为需要大量数据储存空间的AI边缘应用提供支持,例如参考影像以及足够的带宽,以便快速处理资料。他说,RPC DRAM还可以提供外接内存,但仅采用扇入型晶圆级晶粒尺寸封装(FI-WLCSP),使其封装尺寸可以达到很小,而且省去了基板以及任何线键合或覆晶封装步骤。

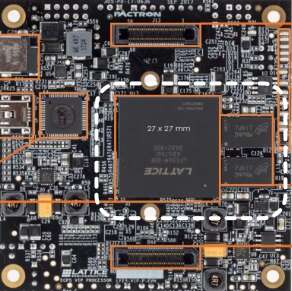

莱迪思半导体(Lattice Semiconductor)看好Etron的这款产品潜力,特别是其精巧的体积以及采用RPC DRAM。Lattice策略营销总监Kambiz Khalilian说,“它可以提供与标准DRAM基本上相同的性能,但接脚数更少。”因此,针对Lattice支持许多攸关性能/折衷的“深度边缘”应用而言,都是理想的选择。它让数据得以在最有意义之处(包括边缘)进行处理,并以小封装与低功耗在带宽不足之处传送所有资料回到服务器进行处理。

Lattice采用Etron以低接脚数、微型化WLCSP封装的RPC DRAM及其高带宽,进一步补强其高性能且小占位空间的FPGA系列。这种微型化的WLCSP封装采用不到传统DDR解决方案一半的讯号。较少的接脚数意味着可以减少内存接口所需要的FPGA资源,并可在较小的pcb组装上占用较小的组件空间。

Khalilian说,某些应用情境的内存需求比Lattice FPGA嵌入的容量更多。 “这就是RPC DRAM得以发挥作用之处。”例如,在许多边缘相机应用中,每平方毫米都很重要。让RPC DRAM更具吸引力之处在于它们可以堆栈在板上,并可根据需要保留Flash的空间,使其不仅可以优化布局,而且还能因应功耗、性能和尺寸之间的折衷。

Objective Analysis首席分析师Jim Handy说,客户已经了解该技术的优点了,并将其整合至产品中,这一事实显示Etron的概念极具潜力。业界也正朝着使用低接脚数的串行接口应用方向发展,但却采用相对较低密度的传统DRAM来因应新兴用例:在边缘内部可处理更多数据——因而能够在装置与服务器场之间尽可能地减少所需的带宽。他并以智慧安全相机设计为例表示,“如果你在相机附近加入了许多智慧,那么你就不需要许多带宽,因为你已足以执行脸部辨识,然后将分析的数据传送回服务器。”

如今,提供低密度DRAM的大多数公司(例如ISSI和Alliance Memory)之所以这样做,都是为了让旧的产品得以持续使用,因为诸如美光科技(Micron Technology)等大型厂商已不再使用旧版内存了。Handy说:“对于专业大厂而言,这一类的需求毕竟太小了。”因此,Etron另辟蹊径,重新思考并重新设计了让人们能以传统密度来使用的产品。“最终的结果是取得了比同级SRAM更便宜的设计,而且还可以放在低接脚数的封装中。”

他说,该公司面临的主要挑战在于如何为该技术创造自己的市场。“由于他们直接瞄准了物联网(IoT),而这一市场确实存在很大的成长空间。”

- 上一条:堡盟工业相机——优化“阴影恢复形状”应用

- 下一条:慧眼科技瓷基板外观检测项目