- 11/23

- 2020

-

QQ扫一扫

-

Vision小助手

(CMVU)

为了发掘宇航市场的潜力,卫星运营商正通过提供增值服务,如超高分辨率成像、流媒体视频直播和星上人工智能,提升星上处理的能力以减少下行链路的需求。从2019年到2024年,高吞吐量载荷的市场需求预计增长12倍,带宽增加至26500 Gbps。

上述的所有应用都和存储器的容量和速度密切相关。实时存储前向高吞吐量载荷基于支持GHz I/O速率的FPGA、存储器、宽带ADC和DAC。例如,一个12位1.5Gsps采样率的ADC每秒产生18Gb的原始数据。一分钟的压缩SAR信息需要大约70Gb的存储容量。这对现有的宇航级存储器解决方案的I/O带宽、访问时间、功耗、物理尺寸和存储容量提出了很大的挑战。

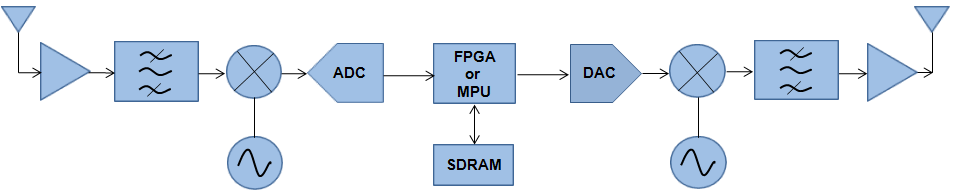

一个数字高吞吐量载荷的典型架构如下图所示。它需要使用一个宇航级FPGA或一个快速微处理器进行星上处理。最新的超深亚微米工艺的经过认证的FPGA一般包含大约30Mb的片上存储器,而CPU会更少。基于这一架构的电信、地球观测和科学载荷多使用Xilinx的XQRKU060、Microchip的RTPolarFire或NanoXplore的宇航级FPGA,需要额外的快速片外存储器存储这些应用产生的大量数据。

图1 数字高吞吐量载荷的架构

实时处理,结合大带宽数据的快速压缩和存储,是下一代高吞吐量卫星服务所必需的。问题是如何找到一款合适的有足够容量、速度和可靠性的宇航级大容量存储器。

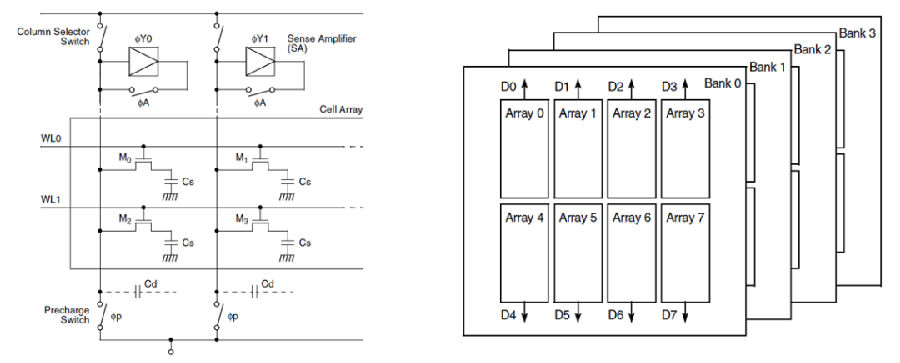

SDRAM是一种快速大容量的半导体技术,它由单元的逻辑阵列和基本的存储元件组成,每个存储元件都包括一个电容和一个FET组成的控制门电路。每个单元存储一个比特,下图是一个简单的4比特存储器。每一行的电压控制晶体管的通断,并对相关的电容充电或放电。在每个所需的“字线”充电之后,列选择器选择对应的电容,准备接下来的读/写操作。由于自放电效应,这些单元必须周期性刷新,包括读和数据写回的操作。

图2 SDRAM位单元和SDRAM芯片的组织结构

SDRAM架构包含许多存储单元,这些存储单元组成行和列的二维阵列。要选择某一个比特,需首先确定对应的行,然后确定对应的列。当对应的行开启时,可以访问多个列,从而提高连续读/写的速度并降低延迟。

为了增加字容量,存储器使用多个阵列,这样当需要进行一次读/写操作时,存储器只需要寻址一次访问每个阵列中的1个比特。

为了增加存储器的整体容量,SDRAM的内部结果还包含多个bank,如上图所示。这些bank互相交织,进一步提高了性能,并可以独立寻址。

当需要执行读或写操作时,首先存储器控制器发出ACTIVE命令,激活对应的行和bank。操作执行完毕后,PRECHARGE命令关闭一个或多个bank中的一个对应的行。