- 08/17

- 2017

-

QQ扫一扫

-

Vision小助手

(CMVU)

传统测量频率的方法主要有直接测量法、分频测量法、测周法等,这些方法往往只适用于测量一段频率,当被测信号的频率发生变化时,测量的精度就会下降。此文是关于一种基于等精度原理的测量频率的方法,在整个频率测量过程中都能达到相同的测量精度,而与被测信号的频率变化无关。本文利用FPGA(现场可编程门阵列)的高速数据处理能力,实现对被测信号的测量计数;利用单片机的运算和控制能力,实现对频率、周期、脉冲宽度的计算及显示。

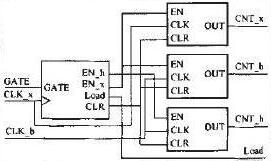

等精度测量原理等精度测量的一个最大特点是测量的实际门控时间不是一个固定值,而是一个与被测信号有关的值,刚好是被测信号的整数倍。在计数允许时间内,同时对标准信号和被测信号进行计数,再通过数学公式推导得到被测信号的频率。由于门控信号是被测信号的整数倍,就消除了对被测信号产生的士1误差,但是会产生对标准信号士1的误差。如图1所示。

图1 等精度测量原理

系统中,如果采用的标准信号源的精度很高,就叮以达到一个很高的测量精度,一般情况下都是采用晶体作为标准信号源,因此可以达到很高的精度,满足一般系统的要求。

1、FPGA模块设计

本系统在传统的等精度测量原理基础上进行了改进和优化。增加了测量占空比的功能,同时由FPGA内部产生清零信号,节省了资源。改进后的FPGA核心模块如图2所示。FPGA部分主要由门控信号产生模块、计数器控制模块、计数器模块、锁存器、中断输出、数据选择输出、顶层模块组成。

图2 等精度测量核心结构

1)门控信号为了测量频率为1H:的信号,要求系统的开门时间不小于1s;同理,为了测量0.1H:频率的信号,要求开门时间最短为109。但是如果系统一直采用10s的门控信号,测量高频信号的等待时间太长,显然不合理,因为测量结果的显示必须要等到一个测量周期结束之后才能更新。本系统采用的方法是,由单片机给FPGA提供一个门控的选择信号,如果FPG人测得的频率小于1Hz,那么单片机自动给出一个启动10s门控的控制信号;反之,如果发现测量的频率大于1Hz,自动切换回1。门控,实现了一个闭环的自动控制,很好地解决了门控的时间问题。

2)计数器控制模块

该模块是本文的创新点所在,主要用来同步被测信号。由前面的分析可知,门控信号启动(上升沿)后,在被测信号的上升沿启动计数允许模块,允许计数器计数;门控信号关闭(下降沿)后,在被测信号的下一个上升沿关闭计数允许模块,停止计数,从而保证了门控信号是被测信号的整数倍,达到了等精度的目的。该模块有GATE,CLKx这2个输人端;ENh,ENx,Load,CLR这4个输出端。GATE为上一级给出的门控信号汉LKesx为被测信号;EN-h,高电平期间对标准信号进行计数,得到CNT_h;EN_x为给出的允许计数信号,在EN-x的高电平期间,对被测信号、标准信号同时计数,得到CNT-x,CNT-b;Load为锁存信号;CLR为计数器清零信号。

由CNTx和CNT_b可以计算出被测信号的频率和周期;由CNTex和CNTh可以计算出被测信号的脉冲宽度。如图3所示。

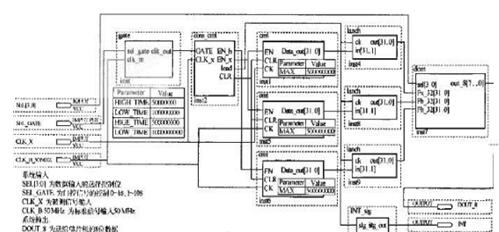

图3 quartus仿真

3)计数器模块

在设计计数器的过程中需要注意计数器的宽度设置,系统中采用的最大门控时间为10a,标准信号源的频率为50MHz,则在计数的允许时间内计数的最大值为:536870912,为了方便数据传输,系统中采用了32位位宽的计数器。

4)锁存器模块

在门控信号关闭的同时,停止计数,同时启动锁存模块,把测量的数据锁存起来,以便传输。

5)中断输出

锁存数据的同时,给单片机一个低电平的中断信号,通知单片机读取数据。

6)数据选择输出模块

系统中采用了3个32位的计数器,由于单片机采用的是51系列单片机,只有8位的数据总线,所以一次通信只能传输8位数据,3x32/8二12,所以设计了一个数据输出控制模块,由单片机提供4根地址线,译码后可以选择16组数据,单片机得到中断通知后,分12次读取测量的数据。

7)顶层模块

实例化所有的底层模块,同时为了调试方便,加入了一些测试点。FPGA部分的整体结构图如图4所示。

图4 FPGA整体结构

2、单片机模块控制

2.1理论分析

在计数允许EN-x时间内,对被测信号和标准信号同时进行进行计数,得到CNT_x和CNT_b,设被测信号的周期为T,,频率为Fx,标准信号周期为F6.频率为Fb。则有:

系统中采用式(6)一式(8)进行计算,得到最终的测量数据,单片机中采用浮点数进行运算,计算的精度可以满足系统的要求。

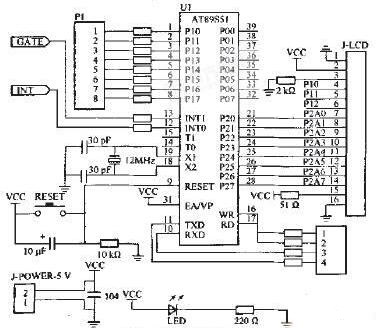

2.2硬件电路

系统硬件电路比较简单,就是单片机的最小系统加上液晶显示模块,设计时需要注意,51单片机端口电压是5V输出,而FPGA是3.3V输出,所以在数据传输时要串联一个电阻一般1000一300f2即可。电路原理图如图5所示。

图5 单片机器部分电路

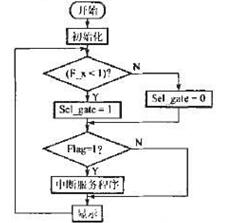

2.3软件设计

单片机软件主要由系统初始化、数据传输、频率、周期、占空比计算、液晶显示等程序模块组成。

下面简单介绍主函数及计算子函数。软件流程如图6所示。

图6 系统流程

中断服务子程序如图7所示。

图7 中断服务子程序

本系统设计采用FPGA和单片机结合的方式实现等精度测量频率,充分发挥了FPGA高速的数据处理能力以及单片机的计算、控制能力。采用Verilog硬件描述语言对系统进行仿真测试.最终下载到FPGA内部。单片机采用C语言编写程序,利用浮点数进行计算,精度高。同时设计了门控信号自动选择的闭环控制,大大地提高了系统的性能。等精度测量技术在生产、实验等环境中得到了广泛的应用。

- 上一条:基于无线技术的下一代医疗视频监控系统设计

- 下一条:详解机器视觉照明重点内容