- 06/15

- 2023

-

QQ扫一扫

-

Vision小助手

(CMVU)

多年来,CMOS成像技术为各类视觉应用实现了更低功耗、更低成本的高速成像。这些图像传感器速度更快,因此能够提高提高工厂车间的检查效率和生产率,并推动机器视觉客户的需求。电信市场对带宽不断提高的要求推动着光纤技术向更大的带宽和更低的功耗发展。而FPGA供应商专门开发相应的技术以满足这一不断增长的电信带宽要求。Camera Link High Speed(CLHS)1.2版认识到了市场对成本改良以及速度的需求,因而为其X协议引入了25 Gbps的速度。有了这一速度上的提升,CLHS便成为了提供0时基误差双向触发和极低延迟(<0.5 µs)双向通用输入/输出(GPIO)的唯一标准。

向后兼容10G

更令人欣喜的是,CLHS 25 Gbps (25G)向后兼容10 Gbps (10G) CLHS。25G的光学引擎也能以10G的速度工作,并且CLHS发现进程定义的起始速度就是10G。开机后,相机和图像采集卡以10G的速度启动,并建立命令通道。随后,图像采集卡读取强制寄存器表,并了解到相机支持25G速度。于是,图像采集卡根据既定程序命令相机将速度提升至25G,同时舍弃链接。接着,相机和图像采集卡以25G速度重新建立链接。若在一段时间后未能建立链接,则这两台设备会恢复至10G,并以故障安全模式重新建立链接。

从10G提速至25G的过程中,知识产权(IP)的核心(或者说复用逻辑的大部分)始终保持不变,1.2版的所有规则相较于旧版本而言也为发生任何变化。CLHS是一个十分稳定的产品开发平台。向后兼容的特性意味着,您可以开发25G的产品并将其与更加成熟的10G产品结合使用,进而减少新协议技术带来的调试风险。对于已经安装10G产品的客户而言,他们可以对相机或图像采集卡进行升级,同时继续使用已有的设备和光纤电缆,既能保留10G产品的低成本优势,又能与25G CLHS产品“混搭”。为了实现对25 Gbps速度的支持,CLHS 1.2加入了SFP+ (10G)、QSFP+ (10G)、SFP28和QSFP28/MPO光纤连接器。电信市场中,SFP28和QSFP28的价格、功耗还在不断下降。现成的MPO (QSFP+/28) - 四芯LC电缆让采用QSFP/MPO连接器的相机能够与已有的四芯SFP+图像采集卡连接。

CLHS最多支持八根电缆,对于QSFP28而言相当于800 Gbps,约96 GByte/秒的有效数据通量。CLHS还支持通过在图像接缝上提供额外数据来向单个处理引擎发送数据,从而并行处理之间的相互独立。协议中的设施会与多个图像采集卡进行同步,确保能够正确取回低带宽处理的图像,并将其组合成完整图像。

CLHS PCS采用64/66编码和前向纠错技术,可在10G速度下实现1200 Mbyte/秒/通道的有效带宽,在25G速度下实现3 GByte/秒/通道的有效带宽。CLHS是所有基于数据包的标准中协议开销最低的一个,其前向纠错技术最多可在2000比特内一次性完成11比特的修正。每种消息类型都会被指定一个优先级。优先级较高的消息会中断低优先级消息的处理,只有高优先级的消息处理完成,低优先级的消息才会继续。这种处理方式优化了带宽的利用率,同时也降低了触发和GPIO信号的延迟。

FPGA实现

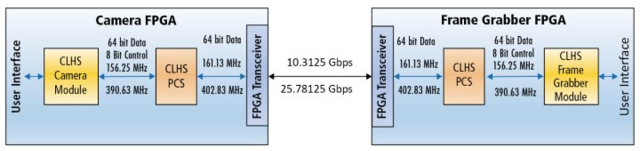

使用A3的IP核可以轻松实现CLHS产品的开发。该核以VHDL源代码的形式交付,由专门的志愿者提供支持。该核心由X IP核和PCS(物理编码子层)组成,同时适用于相机和图像采集卡。下图展示了连接总览以及FPGA在10G、25G下的工作频率。采用25G串行解串器的FPGA可以前向纠错PCS的402 MHz运行速率关闭时序。

FPGA fabric以10G和25G速度运行时的CLHS IP core顶层总览。由Teledyne Dalsa友情提供

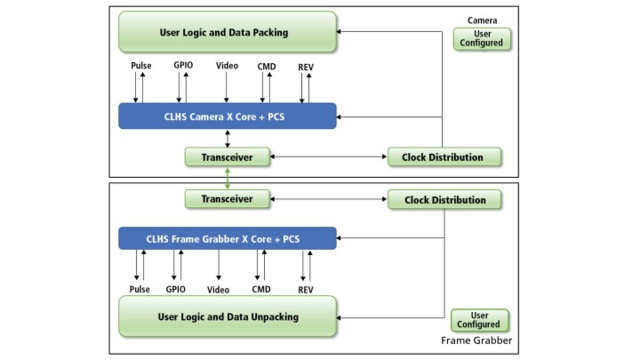

核心和PCS不涉及任何厂商指定的模块或视频、命令通道块随机存储器。CLHS IP已被汇编进Xilinx(赛灵思)(AMD)、Alter(阿尔特拉)和PolarFire的FPGA中。用户负责锁相回路(PLL)和收发器功能的实例化。图2给对核心特性和用户责任进行了更详细的说明。

如前所述,开机识别是10 Gbps的特性,但若电缆两端合适,也可转移至25 Gbps上。在FPGA实现层面,这意味着64对1收发器首先以161.13 MHz的交换接口速度运行,当协商出更高的速度、舍弃链接并重新连接时,交换接口速度会变为402.83 MHz。不同的FPGA会提供不同的方法来实现速度变化,但接口始终为64对1。通常而言,需要通过锁相回路(PLL)来获取161.13 MHz时钟,并创造出156.25 MHz时钟。新的交换速度达到稳定后,需要重置锁相回路。

IP核特性保持不变

如图2所示,核心上有五条虚拟通道是向用户逻辑开放的。若用户不需要某一项功能,如相机向主机发送GPIO等,可将模块输入绑定至低位、将发送请求绑定至地位,那么综合工具就会将这些资源消除。脉冲(触发器)、GPIO和修订消息与TX/RX时钟空间(156/390 MHz)同步,当需要发送数据或在关联通道上接收数据时,提供并行输入/输出(I/O)端口对一个时钟的一个数位进行断言。

视频和命令通道是在用户定义的时钟I/O上运行的,后者可根据用户系统进行优化。命令通道具有“保证”交付特性,并在链路层受到流控制。PCS具备纠错功能,但与只有错误检测与数据重发的M协议相比,X协议还包括了针对命令通道的CRC错误检测和自动数据重发功能,可不断尝试发送命令消息,最高可发送10次。用户要通过命令通道的写入使能控制将通用控制协议(GenCP )和GenIcam数据写入命令缓冲区,当命令完成后,对一个命令时钟周期的命令发送请求输入进行断言。CLHS IP核会对TXcommandBusy信号进行断言,并将命令消息安排在脉冲(触发器)、链路层确认、GPIO和视频消息之后传输。接收器收到消息无误后,CLHS IP会返回确认消息,告诉发送器取消重发超时并等待。若接收器返回未确认消息,则发送器会再次发送消息。接收消息的微控制器收到消息有效频闪灯的新消息提示后,从命令缓冲区读取消息,导致CLHS IP向缓冲区发送一条空的确认消息。因此,TXcommandBusy信号被重置,以确保链路层的流控制。GenCP还规定,不论情况如何,一次应仅处理一条消息,且每次交易以GenCP状态确认或请求数据作为结束的标志。

CLHS IP核用户界面。由Teledyne DALSA友情提供

视频消息也需要用到缓冲区,且在读写功能的作用下可将消息存入核心或从核心取回消息。与命令消息类似,发送请求或新消息准备脉冲会受到断言。但与命令通道不同的是,视频不具备自动重发功能,因为前向纠错特性已足够处理偶发的传输错误。

为满足客户对更高速度的需求,CLHS 1.2版允许使用25G电信技术。向后兼容特性让开发者能够在提速以前利用更成熟的10G产品对新产品的运行进行验证,从而达到降低25G调试风险的目的。通过低成本的10G产品与25G产品的混搭,客户可以对检测系统的成本进行优化。在未来,CLHS委员会计划以现有的X核作为技术基础向50G转型,将发展路径上的风险控制在较低水平。

(作者:Mike Miethig,Teledyne DALSA技术经理;CLHS标准技术附属委员会主席)