- 01/19

- 2006

-

QQ扫一扫

-

Vision小助手

(CMVU)

基于TMS320DM642的H.264视频压缩系统

卢少平1 王洪燕2 沈庆浩1

(1.华东理工大学,上海,200237;2.上海迅特电子科技有限公司,上海,200031)

摘要:简单介绍了H.264采用的新编码技术。结合DSP硬件开发方法,以TI DM642为处理平台,实现了H.264视频压缩系统。

关键词:视频编码;H.264;DM642;DSP

Abstract:This paper has given a brief introduction to the new encode technology adopted by H.264, and implemented a H.264 video compression system based on DM642 with the method of DSP hardware development.

key words: Video Coding;H.264;DM642;DSP

1 引言

随着互联网的广泛应用和数字化技术的高速发展,实时视频和数据信息交流已经成为人们日常生活中越来越依赖的沟通方式。H.264作为视频编码最新国际建议标准,提供了更好的压缩性能和网络自适应性,具有广阔的应用前景。与此同时,由于H.264编码算法复杂,采用DSP高速处理器来进行编码能够比较好的提高编码效率。本文介绍了一种基于DM642芯片实现的H.264视频压缩系统。

2 H.264标准的主要技术

国际电信联盟ITU-T视频编码专家组(VCEG)和国际标准化组织ISO/IEC的动态图像专家组(MPEG)是目前两个制定视频编码标准的国际组织。自2001年起,VCEG和MPEG共同组成了合作开发小组JVT,在H.26L的基础上开发新一代视频编码标准:H.264,同时将它将作为MPEG-4标准的第10部分[1]。H.264的主要目的在于增强压缩性能的同时为诸如视频会议、数字媒体存储、电视广播和流媒体等各种传输环境下提供网络友好性。

与以前的MPEG-4和H.263标准相比,H.264主要在以下方面有了重要改进:

(1) 编码系统分为视频编码层(VCL)和网络抽象层(NAL)。VCL由运动补偿、系数变换编码、熵编码等编码技术,提高了视频的编码效率。NAL能根据每个特定的网络环境,从而更灵活的将编码数据组合到网络中[2];

(2) 采用灵活的运动补偿预测算法。在H.264中,使用了帧间和帧内两种不同的预测模式提供合适的预测方法,其中包括将宏块分割为4*4等可变大小分块等;

(3) 引入了块间滤波系统。在编码和解码中使用块滤波系统,使变换产生的误差边界被平滑,提高了主观效果,并避免了误差导致的积累引起图像质量降低;

(4) 基于1/4和1/8象素精度的运动估计。H.264扩展了象素精度的运动估计,通过相邻象素使用更复杂的估计算法得到更准确的估计值,同时引入了更大的运算复杂度;

(5) 使用了多预测参考帧。为了去除帧间时间相关性,在以往的压缩编码系统如MPEG-4中,采用的是IBBPBBP帧的预测编码模型。而在H.264中,使用了最多达到I帧后面有五个P帧的后续预测参考帧,从而使帧间预测可选范围更大,预测也更准确;

(6)采用了基于信息量分别采用全局变长编码(UVLC)和基于语法的自适应算术编码(CABAC)等熵编码技术。CABAC效率更高,但需对已编码符号进行统计进行不断的调整,运算量比较大[3];UVLC虽然位率较高效率低下,但计算复杂度较低,适用于对编码时间要求很严格的应用中;

(7) 引入了SP Slice技术,用于不同码流的切换、随机访问和错误恢复等目的。

H.264编码算法复杂, 需要存储和运算的数据量非常大,在存储空间分配、数据传输、和运算速度上要求很高。可以说,H.264编码效率之所以如此之高,是以牺牲运算复杂度为代价的。

3 DM642的特点

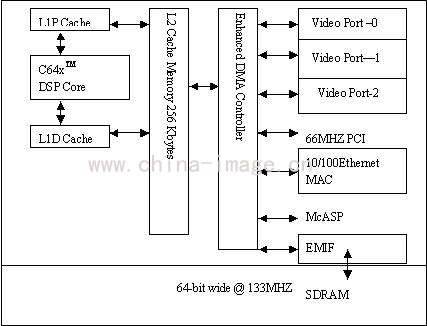

图1 DM642处理器框图

Figure.1. TMS320DM642 DSP Block Diagram.

DM642是TI公司的高性能视频/图象处理DSP,采用了现今著名的并行体系结构:超长指令字VLIW(Very Long Instruction Word)结构,可以在每个周期执行八条32bit的指令,具有很强的并行运算能力。该DSP处理器框图如下所示,基于C6000系列的C64x CPU,采用了增强型VelociTI.2TM架构,扩宽了读取/存储数据路径和二级缓存,可以在视频处理的关键之处使每个周期通过增加新的指令来加速,从而能够更好的提高处理性能[4]。

DM642的存储器采用程序存储器和数据存储器分开的哈佛结构,这些存储器既作为存储器映射,又可作为缓存cache。DM642的增强直接存储器存取控制器EDMA支持中断报告、外设DMA传输和DMA 串接,最高时钟达1/2 CPU CLK,其最大I/O带宽可供64个独立通路达到16G bps。为保持使用低速率、相对便宜的外部存储器,DM642提供有一个64位外部存储器接口(EMIF)和两级片内高速缓冲存储器(Cache)。McASP为多路音频串口,可支持多路音频的模数转换/数模转换(ADC/DAC)。

DM642所集成新的视频口共有三个VP口,可以灵活配置位视频捕捉或视频回放模式。在BT.656和Y/C模式下,每个通道的视频FIFO会分成3个独立区域,分别存放Y、Cb、Cr数据。由视频口和EDMA,每个通道的FIFO分别将这些视频数据实现高速转移。

4 视频压缩系统

4.1系统模块

在该系统中,各个模块如下图所示。PC平台采用Intel主频2.8G的P4 CPU,256M DDR的内存,调试平台为Visual C++ 6.0。DSP为TI DM642。DSP/BIOS的组成分为三部分:抢先多任务的实时内核和对象类型模块化的API、实时分析工具和配置工具。DSP/BIOS提供的线程之间的通信和同步机制,实现了实时调度和同步以及主机与目标系统通信和实时监测的应用。DSK板级支持库BSL(Board Support Library)专门用于配置与控制板卡设备的C语言应用程序API,其各个模块用于构建和存储于库文件当中。PCI Driver通过HPI接口负责将DSP上的编码数据传输至PC主机上。HPI(Host port interface)作为16-bit模式和PCI桥芯片相连。另外主机可以将HPI以从端口的方式直接访问DSP的所有内存空间,这样主机既可以向下发送诸如码率、帧率等参数设置,也可以接收未编码的采集数据从而在主机上实现视频预览。

图2 基于DM642芯片的H.264视频压缩系统

Figure.2. H.264 Video Compression System based on TMS320DM642.

4.2系统流程

在PC机上的程序运行之前,应先装载DSP端的程序。程序启动之后,首先是DM642的视频端口进行视频数据采集。DM642的视频端口外设采集到的视频数据Y、Cb、Cr的抽样比是4:2:2,因此PC平台上可由HPI接收到的预览图象数据也为YUV422格式。DM642视频采集模式支持4:2:2格式的1/2水平缩放、4:2:2格式的色度重采样。下图的视频端口采集模式中,2路RAW模式输入包括2路10位或者1路20位。在双通道RAW模式下,FIFO分为2部分,分别对应于2个通道,每个通道的容量为2560字节。此外其支持的BT.656嵌入式同步模式可实现视频回放。在这种模式下,FIFO分为3部分,分别存储Y、U、V数据。这些灵活高效的FIFO分配方式以及64位高速EDMA传输使EDMA链接时,每个视频FIFO配合各自的EDMA传输通道,成功地实现了高效的数据转移。

图3 视频采集模式

Figure.3. Video Port Block Diagram.

视频端口将该通道32位的FIFO采集到视频数据后,以DMA方式将送入编码器。压缩编码器的输入设定为CIF格式即352*288,帧率为25帧/秒。这里H.264编码器为Baseline Profile级编码,宏块采用I、P两种方式,没有实现B Slice、加权预测和CABAC等算法应用。在宏块级,涉及到运动估计、DCT变换、量化、编码、反量化、运动补偿等。

在DSP完成编码后,可以采取以太网或PCI两种较简单的方式将视频数据传送至PC机端。

由于DM642处理器的以太网口能够在DSP与网络之间提供视频数据10M/100M的高效传输,在我们已开发好的TCP/IP协议基础上,只要采用简单的C语言编写Socket就可以达到DSP与PC主机之间的视频通信。在这里,我们采用PCI通信的方式将视频编码数据传送到PC机上。

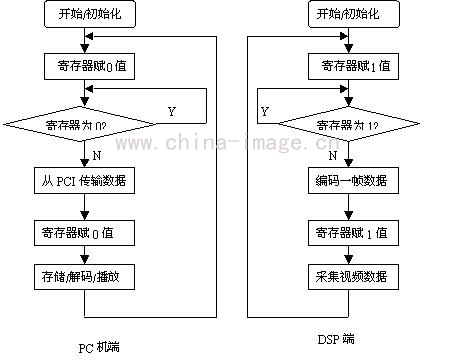

DSP与PC机的中断与同步机制非常重要,因为任何一方的延时等待都可能给系统的实时性造成影响。该系统中,H.264编码器的帧编码与PC传输之间的同步通过一个全局寄存器来实现,设定DSP底层对寄存器值赋值1操作,而PC机则负责对寄存器值赋值0操作。首先,DSP程序初始化,并将该上述寄存器值设为1,接着持续搜索寄存器值,如为1则进行空循环操作以等待PC端的命令。当PC端系统启动时,向下发送消息把寄存器值设为0,接着持续搜索寄存器值,如为0则进行空循环操作以等待DSP编码完一帧数据。此时因寄存器值为0,故DSP首先对采集进来的一帧数据进行压缩编码处理,处理完之后将寄存器值置1并继续空循环等待。由于编码完一帧,寄存器值为1,PC端检测到之后马上将编码数据从PCI传输至PC机上实现播放与存盘等。在处理完编码数据搬移之后,PC端马上又将寄存器值赋0,从而触发DSP实现下一帧的处理。这样,DSP的编码循环和PC机从PCI的数据传输状态机循环,就实现了DSP与PC机两端的数据编码与数据传输之间的同步。

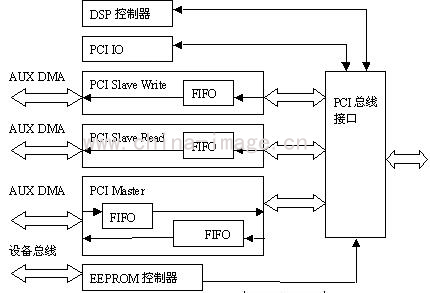

图4 PCI接口框图

Figure.4. PCI Interface Block Diagram.

图5 PC/DSP同步框图

Figure.5. PC/DSP Synchronous Diagram.

5 小结

与纯PC平台相比,DM642处理平台能够极大地改善视频编码的实时效果。本文介绍了基于TMS320DM642 DSP的H.264实时视频压缩系统的设计和实现方案。在此基础上充分利用平台资源,有针对地做出程序结构和算法上的优化(例如局部地改变一些数据类型、程序结构和使用线性汇编来改写核心函数)之后,能够达到比较好的实时效果。

参考文献

[1] Draft ITU-T recommendation and final draft international standard of joint video specification (ITU-T Rec. H.264/ISO/IEC 14 496-10 AVC,in Joint Video Team (JVT) of ISO/IEC MPEG and ITU-T VCEG, JVTG050, 2003.

[2] Thomas Wiegand,Gary J.Sullivan, Gisle Bjøntegaard,et al Overview of the H.264/AVC Video Coding Standard,IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY,VOL.13,No.7,JULY 2003.

[3] Detlev Marpe,Heiko Schwarz,and Thomas Wiegand. Context –Based Adaptive Binary Arithmetic Coding in the H. 264/ AVC Video Compression Standard ,IEEE TRANSCTIONS ON CIRCUITS AND SYSTEMS VIDEO TECHNOLOGY, VOL.13,NO.7,JULY 2003.

[4] TMS320DM642 Technical Overview.TI Application Report SPRU615-September 2002.

[5] 李方慧 王飞 何佩琨 TMS320C6000系列DSPs原理与应用(第二版).电子工业出版社.2003.

[6] TMS 320C6000 CPU and Instruction Set Reference Guide. TI. 2000.10

版权所有,任何个人或机构都不得以任何形式转载,否则追究法律责任,谢谢!