- 06/18

- 2024

-

QQ扫一扫

-

Vision小助手

(CMVU)

芯片测试是极其重要的一环,有缺陷的芯片能发现的越早越好。在芯片领域有个十倍定律,从设计-制造-封装测试-系统级应用,每晚发现一个环节,芯片公司付出的成本将增加十倍!所以测试是设计公司尤其注重的,如果把有功能缺陷的芯片卖给客户,损失是极其惨重的,不仅是经济上的赔偿,还有损信誉。因此芯片测试的成本也越来越高。

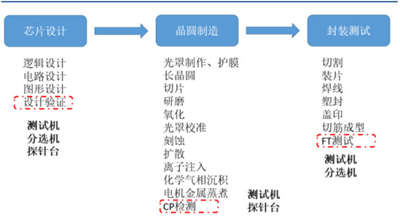

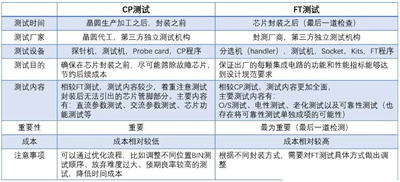

芯片测试分两个阶段,一个是CP(Chip Probing or Circuit Probing)测试,也就是晶圆(Wafer)测试。另外一个是FT(Final Test)测试,也就是把芯片封装好再进行的测试。

芯片CP测试

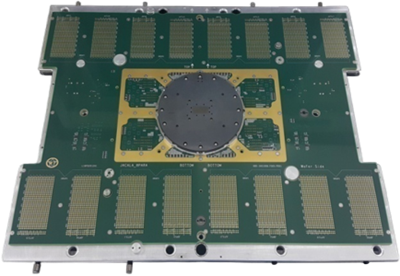

CP测试chip probing(晶圆测试)指的是,在晶圆 Wafer制造之后、封装之前,在未进行划分封装的整片晶圆上通过探针将裸露的芯片管脚和测试机相连,进行的芯片测试步骤。

CP测试在整个芯片制作流程中处于晶圆制造和封装之间。晶圆(Wafer)制作完成之后,成千上万的裸DIE(未封装的芯片)规则的分布满整个Wafer。

由于尚未进行划片封装,芯片的管脚全部裸露在外,这些极微小的管脚需要通过更细的探针台来与测试机台连接。在未进行划片封装的整片Wafer上,通过探针将裸露的芯片与测试机连接,从而进行的芯片测试就是CP测试。

测试对象是针对整片wafer中的每一个Die,目的是确保整片wafer中的每一个Die都能基本满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证。可以用来检测fab厂制造的工艺水平。

晶圆CP测试,常应用于功能测试与性能测试中,了解芯片功能是否正常,以及筛掉芯片晶圆中的故障芯片。CP的难点是如何在最短的时间内挑出坏的die,修补die。常用到的设备有测试机(IC Tester)、探针台(Prober)以及测试机与探针卡之间的接口(Mechanical Interface)。

CP测试主要目的

Robotzone :晶圆被送到封装厂之前,对晶粒电性能参数进行测试,鉴别出合格芯片,提高良率,降低后续封测成本;对器件/ 电路的电性能参数进行特性评估; 由于芯片管脚封在内部,导致部分功能无法测试,所以只能在CP中测试。

芯片FT测试

FT测试Final Test,也叫终测FT,是封装后的成品测试,是芯片出厂前的最后一道拦截。测试对象是针对封装好的chip,CP测试之后会进行封装,封装之后进行FT测试。可以用来检测封装厂的工艺水平。成品测试是对封装后的芯片进行功能和电参数性能测试,保证出厂的每颗集成电路的功能和性能指标能够达到设计规范标准。

FT测试分为两个步骤:

Robotzone :自动测试设备(ATE),一般为几秒钟,成本较高;系统级别测试(SLT)必须项,一般测试时间为几个小时,逻辑较为简单。

FT的难点是如何在最短的时间内保证出厂的Unit能够完成全部的功能。FT测试(成品测试)主要使用仪器为测试机tester(ATE)+分选机 handler + socket。

测试解决方案

随着芯片设计行业的迅速发展,出现了只拥有芯片设计能力,却没有芯片测试实力的公司,于是大量芯片类型被设计了出来之后,就停留在了设计阶段,无法进行封装测试,更别说生产上市了。这就意味着,大量的芯片测试需求没有得到满足,行业内对于芯片测试业务的需求愈发旺盛。“测试”行业悄然崛起!

芯片测试公司则需要根据客户需求,对芯片进行出厂前的测试,客户还能够根据测试反馈,及时调整芯片设计思路,甚至可以定制化地推出测试服务,满足客户对于芯片功能、性能和品质等多方面的严苛要求。

当下,我国在封测领域已屹立于世界前列,相信在国人的共同努力下,我们的芯片设计和制造水平也会有一天能够走向世界,引领时代。

(文章来源于互联网,如有侵权,请联系删文)